Logical instructions are one among the instruction set of 8086 microprocessor. These instructions are also known as Bit Manipulation Instructions. In 8086 microprocessor instruction set, the bit manipulation instructions are divided into three groups. They are,

- Logical Instructions,

- Shift Instructions, and

- Rotate Instructions.

The logical group includes AND, OR, XOR, NOT, and TEST instructions. While the shift instructions group includes SHR, SHL, SAR, and SAL instructions, and rotate instructions include ROL, ROR, RCR, and RCL instructions. In this article let us learn about the logical instructions of the 8086 microprocessor.

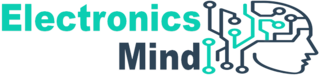

AND Instruction :

The AND instruction performs bit by bit logical AND operation between source operand and destination operand, and stores the result in the destination operand. The logical AND operation gives output as TRUE (logic 1) only when both the inputs are TRUE i.e., logic 1, otherwise, the output will be FALSE (logic 0) as shown in the below truth table.

The limitations of AND instruction are source operand or destination operand must be a register or memory location. The two operands should not be memory locations or immediate data in the same instruction. The destination operand should not be immediate data. The below shows the syntax of AND instruction execution,

Example for AND Instruction :

| Instruction | Explanation |

|---|---|

| AND BL, AL (Register, Register) | ; AL = 1001 0011 = 93H ; BL = 0111 0101 = 75H ; AND byte in AL with byte in BL ; BL = 0001 0001 = 11H |

| AND CX, 00F0H (Register, Immediate value) | ; CX = 0110 1011 1001 1110 ; 00F0H = 0000 0000 1111 0000 = 75H ; AND byte 00F0H with byte in CX ; CX = 0000 0000 1001 0000 |

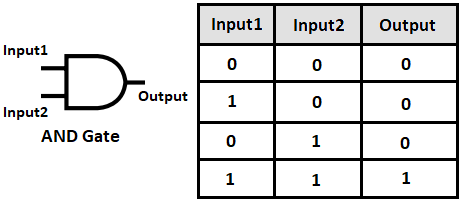

OR Instruction :

The OR instruction performs bit by bit logical OR operation between source operand and destination operand, and stores the result in the destination operand. The logical OR operation gives output as logic 1 when either one of the inputs or both the inputs is given as logic 1. When both the inputs are given as logic 0, then the output will be logic 0 as shown in the below truth table.

The same limitations of AND instruction are applicable to OR instruction. The below shows the syntax of OR instruction execution,OR destination operand, source operand

Example for OR Instruction :

| Instruction | Explanation |

|---|---|

| OR BL, AL (Register, Register) | ; AL = 1001 0011 = 93H ; BL = 0111 0101 = 75H ; OR byte in AL with byte in BL ; BL = 1111 0111 = F7H |

| OR CX, 00F0H (Register, Immediate value) | ; CX = 0110 1011 1001 1110 ; 00F0H = 0000 0000 1111 0000 = 75H ; OR byte 00F0H with byte in CX ; CX = 0110 1011 1111 1110 |

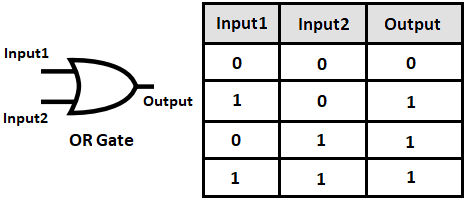

XOR Instruction :

The XOR instruction performs bit by bit logical exclusive OR (XOR) operation between source operand and destination operand, and stores the result in the destination operand. The logical XOR operation returns FALSE only when two inputs are same i.e., either two inputs with logic 0 or with logic 1, otherwise the output will be TRUE as shown in the below truth table.

The limitations of XOR instruction are same as for AND instruction. The below shows the syntax of XOR instruction execution,XOR destination operand, source operand

Example for XOR Instruction :

| Instruction | Explanation |

|---|---|

| XOR BL, AL (Register, Register) | ; AL = 1010 1111 = AFH ; BL = 1111 0000 = F0H ; XOR byte in AL with byte in BL ; BL = 0101 1111 = 5FH |

| XOR AX, 0098H (Register, Immediate value) | ; AX = 0011 1111 0000 1111 = 3F0FH ; 0098H = 0000 0000 1001 1000 ; XOR byte 0098H with byte in AX ; AX = 0011 1111 1001 0111 |

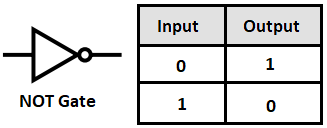

NOT (Complement) Instruction :

The NOT instruction complement (invert) the elements of the operand (register or memory location) in a bit-wise manner. It gives output as FALSE if the input is TRUE and vice versa as shown in below truth table.

No flags of the 8086 microprocessor are affected by NOT instruction. The below shows the syntax of NOT instruction execution,NOT operand

Example for NOT Instruction :

| Instruction | Explanation |

|---|---|

| NOT AX | ; AX = 0010 0000 0000 1111 ; performing NOT on AX ; AX = 1101 1111 1111 0000 |

| NOT AL | ; AL = 0110 1100 ; performing NOT on AL ; AL = 1001 0011 |

TEST Instruction :

The TEST instruction performs bit by bit logical AND operation on the source and destination operand but does not load the destination operand with result i.e., this instruction performs bit by bit AND and sets the corresponding Flag. Hence TEST instruction only affects the flag register (OF, CF, SF, ZF, PF) and AF undefined which indicates the result of the operation without changing any operand. This is normally used to compare the operands bit by bit.

Example for TEST Instruction :

| Instruction | Explanation |

|---|---|

| TEST AL, CL | ; AND CL with AL ; Flags are affected, result is not stored |

| TEST AX, 0800H | ; AND 0800H with AX ; Flags are affected, result is not stored |